APRIL Issue 7/2011

Tales from the Cube: Band together Pg 56

EDN.comment: The 3-D IC and you Pg 8

Signal Integrity: Whang that ruler Pg 16

Design Ideas Pg 45

Make your electronics supply chain green or else Pg 52

CORPORATION 1

Expert and professional cutting edge solutions.

digikey.com/techzone

# Hello future.

Goodbye status quo.

# Oscilloscopes Redefined Starting at \$1,230\*

© 2011 Agilent Technologies, Inc. \*All prices are in USD and subject to change

|                                    | X-Series<br>(MSO and DSO) | TDS2000C<br>Series (DS0) | X-Series<br>(MSO and DSO) | MSO/DP02000<br>Series |

|------------------------------------|---------------------------|--------------------------|---------------------------|-----------------------|

| Bandwidth (MHz)                    | 70, 100, 200              | 50, 70, 100, 200         | 100, 200, 350, 500        | 100, 200              |

| Max sample rate                    | 2 GSa/s                   | 2 GSa/s                  | 4 GSa/s                   | 1 GSa/s               |

| Max memory depth                   | 100 kpts                  | 2.5 kpts                 | 4 Mpts                    | 1 Mpt                 |

| Max update rate<br>(waveforms/sec) | 50,000                    | 200**                    | 1,000,000                 | 5,000                 |

| Fully upgradable                   | Yes                       | No                       | Yes                       | No                    |

| Function Generator                 | Yes                       | No                       | Yes                       | No                    |

|                                    |                           |                          |                           |                       |

\*\*Refer to Agilent Pub 5989-7885EN for update rate measurements

Data for competitive oscilloscopes from Tektronix publications 3GW-25645-0 and 3GW-22048-1

Measurements taken on same signal using Agilent MSOX2024A and Tektronix TDS2024B

Screen images are actual screen captures and scopes are shown to scale

Agilent and our Distributor Network Right Instrument. Right Expertise. Delivered Right Now.

Notes:

Buy from an Authorized Distributor www.agilent.com/find/distributors

See the difference today. www.agilent.com/find/redefined

570,000+ PRODUCTS IN STOCK 470+ SUPPLIER PARTNERS NEW PRODUCTS ADDED DAILY The industry's broadest product selection available for immediate delivery

**www.digikey.com** 1.800.344.4539

Digi-Key is an authorized distributor for all supplier partners. New products added daily. © 2011 Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

# Multi-lane Jitter Tolerance running too slow?

# Let Centellax Save You Time

If testing jitter tolerance in multi-lane devices or high channel count SERDES with a single serial BERT gives your test technician plenty of time for more exciting things, like watching plants grow, look to Centellax to speed things up. Our Parallel Channel BERT measures Jitter Tolerance on ALL lanes simultaneously, at a surprisingly low cost that won't break your capital budget.

# **Speed Up Your Testing**

Minimize cable loss with remote pattern generator and error detector heads that can be mounted close to your device under test. 4-tap de-emphasis is integrated directly in the pattern generator head, eliminating the need (and cost) of a dedicated de-emphasis processor. Our Signal Integrity Studio software ties it all together, including a parallel jitter tolerance test with unlimited channel count.

When you are ready to speed up your testing, come see us at www.centellax.com.

**Affordability** without compromise

For more information on Centellax products visit **www.centellax.com**

# **ARM** versus Intel: a successful stratagem for RISC or grist for CISC's tricks?

ARM and its licensees are striving to expand their overall market presence by tackling Intel's x86 in servers and client desktop and laptop computers. Intel has responded by attacking ARM on its own turf: handsets, tablets, and the like.

> by Brian Dipert, Senior Technical Editor

# EDN 4.7.11 contents

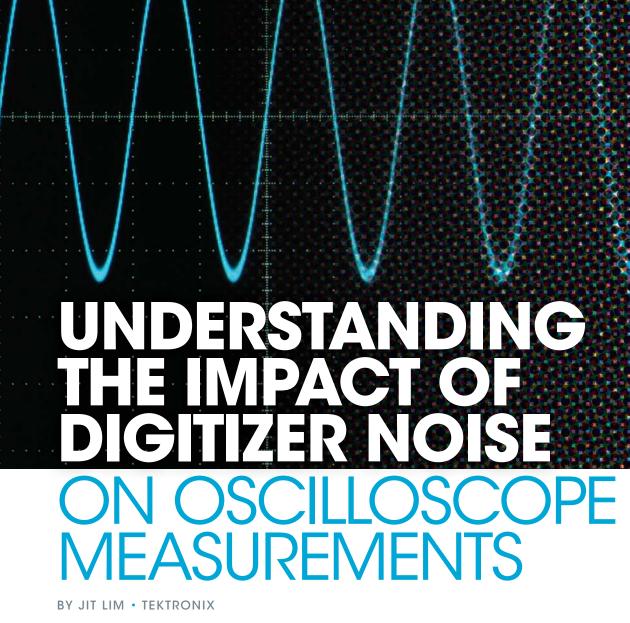

# **Understanding the** impact of digitizer noise on oscilloscope measurements

→ O How closely does the output of any ADC, waveform digitizer, or DSO follow an analog input signal? ENOB testing provides a means of establishing a figure of merit for dynamic digitizing performance.

> by Jit Lim, **Tektronix**

# Innovative circuit designs target performance improvement and differentiation

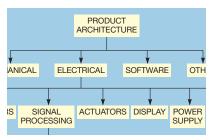

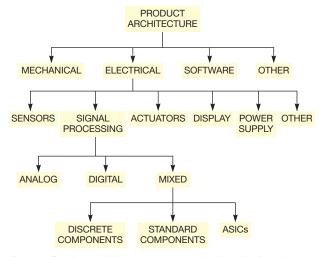

Product innovation is the path to product rejuvenation. A holistic approach compels designers to consider innovation at all architectural levels. Product designers and ASIC designers can together achieve innovation breakthroughs. by Eugene R Bukowski, Jr, Accenture

- 10 AWG boasts 14-bit resolution, 12G-sample/sec updates

- 11 Next-generation solid-state drives tout 6-Gbps SATA speeds

- 11 LED array enables small-formfactor MR-16 replacements

- 12 Researchers claim millimeterscale computing system

- 12 AVX offers Spice models for tantalum, niobium-oxide capacitors

- 13 Eight-channel analog multiplexer meets high-reliability military specs

- 13 Tool for custom-IC design allows verification in real time

- 14 Lithography reduction yields design simplicity

# The e-reader paradox

E-book readers require high performance, even to just display text.

> by Franck Nicholls. Freescale Semiconductor

COVER: COMPOSITE IMAGE BY TIM BURNS. GLOVE: INKTYCOON/ISTOCKPHOTO.COM; FLAMES & BACKGROUND: SUSARO/ISTOCKPHOTO.COM

# ESIGNIDEAS

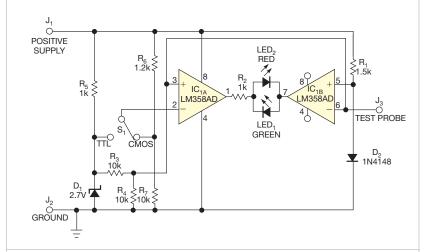

- Low-component-count logic probe works with TTL and CMOS logic

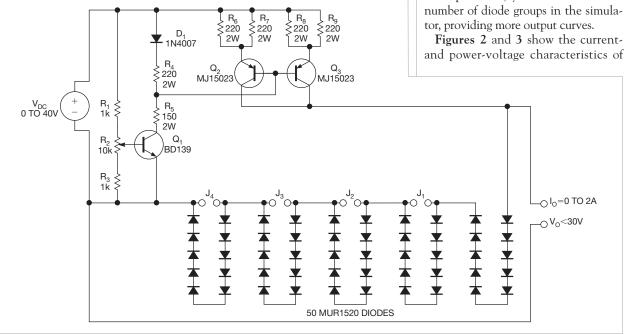

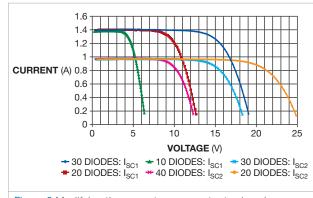

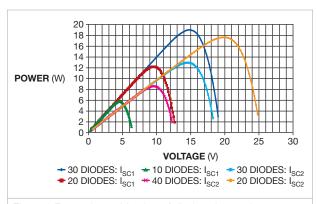

- Circuit implements photovoltaic-module simulator

- Switch circuit controls lights

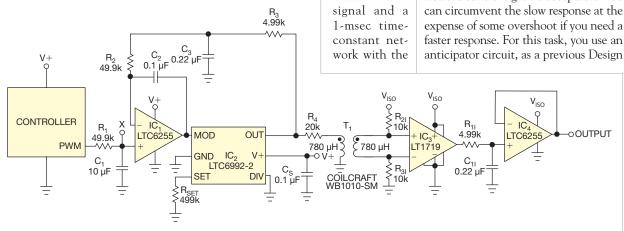

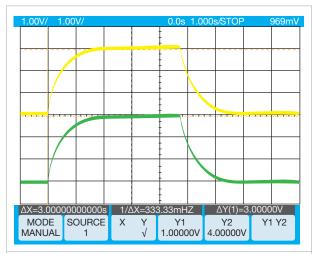

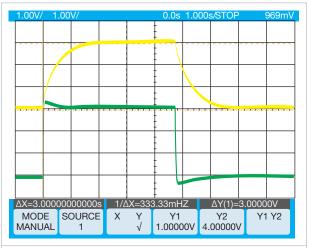

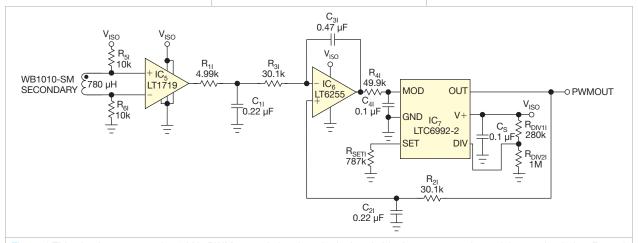

- Isolated PWM suits low frequencies

Fast and Accurate component testing

# LCR meters starting at \$995

- Basic Accuracy: 0.05% (SR720), 0.2% (SR715)

- Test frequencies: to 100 kHz (SR720), 10 kHz (SR715)

- Up to 20 measurements per second

- Measures R, L, C, Q and D

- 100 mV to 1.0 V test signals

- Internal bias to 2 V, external bias to 40 V

- RS-232 computer interface

- Kelvin clips, surface mount tweezers, 4-wire adaptor (opt)

- GPIB and Parts Handler Interfaces (SR720)

m e a s u r e passive components with up 0.05% precision. These simple to use instruments are perfect for incoming inspection, automated testing and general benchtop use. The convenient auto measure feature, binning capabilities for part sorting, and quick and easy calibration simplify test procedures. Standard RS-232, GPIB and Parts Handler interfaces make automated testing a snap. For fast, accurate component testing, the SR715 and SR720 offer

**LCR**

<u>M</u>eters

from SRS

SR715....\$995 (US 1151) SR720....\$1495 (US 1151)

Stanford Research Systems

1290-D Reamwood Ave, Sunnyvale, CA 94089 Phone (408) 744-9040 e-mail: info@thinkSRS.com • **www.thinkSRS.com**

unmatched value.

# contents 4 711

# **DEPARTMENTS & COLUMNS**

- 8 EDN.comment: The 3-D IC and you

- 16 Signal Integrity: Whang that ruler

- 52 Supply Chain: Make your electronics supply chain green—or else

- 54 Product Roundup: Discrete Semiconductors; Amplifiers, Oscillators, and Mixers

- 56 Tales from the Cube: Band together

# **EDN**) online contents

www.edn.com

# **ONLINE ONLY**

# JOIN THE CONVERSATION

Connect with the more than 2700 engineers and executives exchanging ideas in *EDN*'s Electronics

Design Network on LinkedIn.

→www.edn.com/110407toca

# Readers' Choice

Here is a selection of recent articles and blog posts receiving high traffic on www.edn.com:

# Baking LEDs in the oven: the Pharox 6W LED bulb

→www.edn.com/110407tocb

# Counterfeiting continues to grow, but the industry fights back

→www.edn.com/110407tocc

# Build accurate Spice models for low-noise, low-power precision amplifiers

→www.edn.com/110407tocd

# Tablet success to infringe on PC sales

→www.edn.com/110407toce

#### Researchers aim at roomtemperature spintronic computers

→www.edn.com/110407tocf

EDN® (ISSN#0012-7515) is published semimonthly, 24 times per year, by UBM Electronics, 11444 W. Olympic Blvd., Los Angeles, CA 90064-1549; 310/445-4290; FAX 310/445-4299. Periodicals postage paid at Los Angeles, CA, and at additional mailing offices. SUBSCRIPTIONS— Free to qualified subscribers as defined on the subscription card. Rates for nonqualified subscriptions, including all issues: US, \$150 one year; \$250 two years; \$300 three years. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. For telephone inquiries regarding subscriptions, call 763/746-2792. E-mail: EDN®/kmpsgroup.com. CHANGE OF ADDRESS—Notices should be sent promptly to PO Box 47461, Plymouth, MN 55447. Please provide old mailing label as well as new address. Allow two months for change. NOTICE—Every precaution is taken to ensure accuracy of content; however, the publisher cannot accept responsibility for the correctness of the information supplied or advertised or for any opinion expressed herein. POSTMASTER—Send address changes to EDN, PO Box 47461, Plymouth, MN 55447. Canada Post: Publications Mail Agreement 40612608. Return undeliverable Canadian addresses to Pitney Bowes Inc, PO Box 25542, London, ON N6C BB2. Copyright 2011 by United Business Media. All rights reserved. Reproduction in whole or part without written permission is prohibited. Volume 56, Number 7 Pintled in USA).

# Benchmark MOSFETs

# DC-DC Buck Converter and POL Applications

|                    | 463b        |     |                    |  |

|--------------------|-------------|-----|--------------------|--|

| S                  | <b>SO-8</b> |     | 1111               |  |

| Part               | V           | nC  | $\mathbf{m}\Omega$ |  |

| IRF8252PBF         | 25          | 35  | 2.7                |  |

| IRF8788PBF         | 30          | 44  | 2.8                |  |

| IRF8721PBF (Cntrl) | 30          | 8.3 | 8.5                |  |

| IRF7862PBF (Sync)  | 30          | 30  | 3.7                |  |

# POFN (5x6

| PUFN (5x6)            |    |     |     |

|-----------------------|----|-----|-----|

| Part                  | V  | nC  | mΩ  |

| IRFH7928TRPBF         | 30 | 40  | 2.8 |

| IRFH7921TRPBF (Cntrl) | 30 | 9.3 | 8.5 |

| IRFH7932TRPBF (Sync)  | 30 | 34  | 3.3 |

| IRFH7934TRPBF         | 30 | 20  | 3.5 |

| IRFH7914TRPBF (Cntrl) | 30 | 8.3 | 8.7 |

IRFH7936TRPBF (Sync)

| PQFN (3x3)    |    |     |                    |

|---------------|----|-----|--------------------|

| Part          | V  | nC  | $\mathbf{m}\Omega$ |

| IRFH3702TRPBF | 30 | 9.6 | 7.1                |

| IRFH3707TRPBF | 30 | 5.4 | 12.4               |

|               |    |     |                    |

4.8

| D-PAK       |    |    |     |

|-------------|----|----|-----|

| Part        | V  | nC | mΩ  |

| IRLR8743PBF | 30 | 39 | 3.1 |

| IRLR8726PBF | 30 | 18 | 8.4 |

For more information call 1.800.981.8699 or visit www.irf.com

# International Rectifier

THE POWER MANAGEMENT LEADER

# BY RON WILSON, EDITORIAL DIRECTOR

# The 3-D IC and you

ne of the most popular topics for conference sessions lately has been the 3-D IC. Panels and papers cover a huge range of topics, but they come down to three questions: What is a 3-D IC, is it real, and what difference does it make? The question of definition is surprisingly loaded. At a recent panel, speakers divided the world of 3-D ICs into three categories. The first category covers simply stacking up independently designed dice and bonding them together, such as the stack of flash and DRAM dice on the SOC (system-on-chip) die in your cell phone. In the stacking approach, all the dice are pretested standard parts, often simply wire-bonded together using their normal I/O bonding pads, sometimes with a silicon interposer to move signals around for the best wire-bonding layout.

The second category of 3-D ICs starts in the architectural-design phase of the system. Architects and IC designers partition the system according to the best technology in which to implement each block. Logic blocks might go into a 20-nm logic process; bulk memory,

into a DRAM process; and I/Os and other AMS (analog/mixed-signal) blocks, into a large-geometry, higher-voltage process. The team would design one die in each process, optimizing the interfaces among the dice for performance needs and power constraints. They would

then assemble the dice into a stack, using flip-chip technology, interposers, and TSVs (through-silicon vias) to interconnect the blocks. One panelist calls this approach technology partitioning.

In the third category, which you could call true 3-D, designers place each cell not in a plane on one die but

in the 3-D space they create by stacking many dice together. TSVs become just another element in the routing hierarchy. In this mindset, a cell may land in one corner of the third die in the stack—not because of its process technology but simply because that lo-

cation optimizes timing for the nets in the area. You can

imagine the complexity of a placement algorithm that must keep track of the additional delays and space required for the TSVs, the thermal- and mechanical-stress impacts of the cell on its local neigh-

on its local neighborhood, and so on.

Each of these categories has its own drawbacks and benefits. Stacking primarily delivers greater component density for space-constrained boards. Technology partitioning also offers greater density, but it further hints at cost savings and significant performance improvements from

the optimized interdie interfaces. True 3-D promises the most: to take over as Moore's Law dies out, giving you a way to continue to increase transistor density.

What does this mean to designers at the board level? In an ideal world, the three approaches would become viable one after the other, providing a continuum of improving density and performance. There's a lot of work that must occur before we reach that ideal, however.

Clearly, stacking works today, if one partner—typically, a giant foundry—is tightly controlling a small supply chain. Technology partitioning is more problematic. Samsung recently demonstrat-

# Discussions of 3-D ICs come down to three questions: What is a 3-D IC, is it real, and what difference does it make?

ed a wide-I/O DRAM die stacked on a logic die bearing TSVs, showing that this approach is not science fiction. Simon Burke, a Xilinx distinguished engineer, says that his company has internally produced an arrangement that stacks a dense FPGA-logic fabric in one technology atop a lower-density AMS die. Many issues still exist; these issues include diverse tool chains, lack of good TSV models, absence of thermal and mechanical 3-D modeling tools, and lack of standards.

As for true 3-D, neither design nor analysis tools exist to support it, and neither the TSVs nor the necessary die-thinning techniques are ready. KK Lin, Samsung's director of foundry design enablement, hopes that his company will have wide I/Os available to designers in 2013, but true 3-D could still lag years behind that. In short, 3-D will come—but slowly and in waves. EDN

Contact me at ron.wilson@ubm.com.

# EDN

#### ASSOCIATE PUBLISHER, EDN WORLDWIDE

Judy Hayes, 1-925-736-7617; judy.hayes@ubm.com

#### **EDITORIAL DIRECTOR**

Ron Wilson, 1-415-947-6317; ron.wilson@ubm.com

#### MANAGING EDITOR

Amy Norcross

Contributed technical articles

1-781-869-7971;

amy.norcross@ubm.com

#### MANAGING EDITOR—NEWS

Suzanne Deffree Electronic Business, Distribution 1-631-266-3433; suzanne.deffree@ubm.com

### SENIOR TECHNICAL EDITOR

Brian Dipert Consumer Electronics, Multimedia, PCs, Mass Storage 1-916-548-1225; brian.dipert@ubm.com

# TECHNICAL EDITOR

Margery Conner Power Sources, Components, Green Engineering 1-805-461-8242; margery.conner@ubm.com

#### **TECHNICAL EDITOR**

Mike Demler EDA, IC Design and Application 1-408-384-8336; mike.demler@ubm.com

#### **TECHNICAL EDITOR**

Paul Rako Analog, RF, PCB Design 1-408-745-1994; paul.rako@ubm.com

# DESIGN IDEAS EDITOR

Martin Rowe, Senior Technical Editor, Test & Measurement World edndesignideas@ubm.com

#### SENIOR ASSOCIATE EDITOR

Frances T Granville, 1-781-869-7969; frances.granville@ubm.com

## ASSOCIATE EDITOR

Jessica MacNeil, 1-781-869-7983; jessica.macneil@ubm.com

#### **CONSULTING EDITOR**

Jim Williams, Staff Scientist, Linear Technology edn.editor@ubm.com

# CONTRIBUTING TECHNICAL EDITORS

Dan Strassberg,

strassbergedn@att.net

Nicholas Cravotta,

editor@nicholascravotta.com

Robert Cravotta,

robert.cravotta@embeddedinsights.com

#### COLUMNISTS

Howard Johnson, PhD, Signal Consulting Bonnie Baker, Texas Instruments Pallab Chatterjee, SiliconMap Kevin C Craig, PhD, Marquette University

## LEAD ART DIRECTOR

Marco Aguilera

# ASSOCIATE ART DIRECTOR

Tim Burns

# PRODUCTION Jeff Tade.

Production Director

Brian Wu,

Publications Production Manager

Jeff Polman,

Derric Treece,

Senior Production Artists

William Baughman,

Lucia Corona,

Ricardo Esparza,

Production Artists

#### EDN EUROPE

Graham Prophet, Editor, Reed Publishing gprophet@reedbusiness.fr

#### EDN ASIA

Wai-Chun Chen, Group Publisher, Asia waichun.chen@ubm.com Kirtimaya Varma, Editor-in-Chief kirti.varma@ubm.com

#### **EDN CHINA**

William Zhang, Publisher and Editorial Director william.zhang@ubm.com Jeff Lu, Executive Editor jeff.lu@ubm.com

#### EDN JAPAN

Katsuya Watanabe, Publisher katsuya.watanabe@ubm.com Ken Amemoto, Editor-in-Chief ken.amemoto@ubm.com

#### EXECUTIVE OFFICERS

Paul Miller,

Chief Executive Officer,

UBM Electronics

and UBM Canon (Publishing Division)

David Blaza,

Senior Vice President,

UBM Electronics

Karen Field, Senior Vice President, Content, UBM Electronics

EDN. 33 Hayden Avenue, Lexington, MA 02421. www.edn.com. Subscription inquiries: 1-763-746-2792; EDN@kmpsgroup.com. Address changes: Send notice promptly to PO Box 47461, Plymouth, MN 55447. Please provide an old mailing label as well as your new address. Allow two months for the change.

UBM Electronics, 11444 W. Olympic Blvd., Los Angeles, CA 90064-1549; 1-310-445-4200; fax: 1-310-445-4299.

66...they make things simple. Where others find ways to complicate the process, Mill-Max consistently delivers what's needed, when it's needed, with little or no fuss. ??

At **Mill-Max** we do everything we can to make your job easier — from our easy-to-use website to quick-turnaround quotes...responsive customer service and technical support...on-time delivery... free samples...and so much more.

44 Quality is not open to compromise, and Mill-Max components meet our very stringent standards. 97

Our connectors speak for themselves...so do our customers.

To view our Design Guide, new product offerings and request a datasheet with free samples, visit www.mill-max.com/EDN608

# AWG boasts 14-bit resolution, 12G-sample/sec updates

gilent Technologies has added a highresolution, wide-bandwidth, 8- or 12G-sample/sec modular instrument to its AWG (arbitrary-waveform-generator) portfolio. The M8190A enables radar-, satellite-, and electronic-warfare-device designers to make reliable, repeatable measurements and create highly realistic signal scenarios to test their products. Precision arbitrary-waveform generation is necessary for realistic testing of systems for detecting low-flying aircraft and for high-data-rate communications in satellite-communications systems. With resolution as high as 14 bits, the M8190A makes it easy for designers to distinguish between signals and distortion in their test scenarios and to more rigorously stress their devices. The instrument's optional 2G-sample memory lets you create longer and more realistic test scenarios.

"The M8190 allows engineers to approach reality when they create test scenarios," says Jürgen Beck, general manager of Agilent's digital- and photonic-test business. "Because the generator simultaneously offers greater fidelity, higher resolution, and wider bandwidth and produces multilevel signals with programmable ISI [intersymbol interference] and jitter at frequencies to 3 Gbps, customers can create signal scenarios that push their designs to the limit and bring new insights to their analysis."

The M8190A simultaneously offers 14 bits of resolution, as much as 5 GHz of analog bandwidth, and the ability to build realistic scenarios with 2G samples per channel of waveform memory. Compact modular AXIe (Advanced Telecommunications Computing Architecture Extensions for Instrumentation and Test

Express) architecture, which targets use in high-performance instrumentation, reduces system size, weight, and footprint.

Agilent's Measurement Research Lab designed a proprietary DAC for the generator using an advanced silicon-germanium bipolar/CMOS process. The DAC operates at 8G samples/sec with 14-bit resolution and at 12G samples/sec with 12-bit resolution. At 8G samples/sec, the DAC delivers SFDR (spurious-free dynamic range) of as much as 80 dBc (decibels referenced to the carrier). This technology eliminates the trade-off between high resolution and wide bandwidth, so measurements are more reliable and repeatable and you are less likely to misinterpret glitches in the waveforms as analog output. The modular generator, whose US entry price is \$79,000, works in either two- or five-slot AXIe chassis.

## -by Dan Strassberg

# ▶Agilent Technologies,

www.agilent.com/find/M8190.

# - TALKBACK

"I designed some of the first automatic toilet flushers in 1983 so had to deal with sifting microwatts out of a sea of garbage."

—Electronics designer Robert Capper, in *EDN's* Talkback section, at http://bit.ly/himngN. Add your comments.

Fitting into this two-slot enclosure, which connects to a separate laptop, the M8190A AWG provides a combination of high resolution, wide bandwidth, deep memory, and flexible waveform-segment sequencing and programming. It also fits into a five-slot AXIe enclosure, in which a plug-in computer module makes it a stand-alone unit.

Next-generation solid-state drives tout 6-Gbps SATA speeds

oughly 15 months after Micron (www.micron. com) unveiled its 6-Gbps, SATA (serial-advanced-technology-attachment)-supportive C300 solid-state drives and six months after the company followed them with the enterprisetargeted P300 variants, Intel has finally rolled out a 6-Gbps SATA-cognizant solid-statedrive family. Whereas Micron's latest-generation C400 drives employ NAND devices built on a 25-nm process that the company jointly developed with IM Flash Technologies (www.

imftech.com), Intel has chosen the more conservative, although perhaps less costeffective, path of sticking with 34-nm-fabricated flash-memory components.

Intel's 510 series leverages the same Marvell (www.marvell. com) controller that Micron's products use. Rumor has it that Intel's internally developed controllers for earlier-generation

Intel's 6-Gbps SATA-cognizant 510 series of solid-state drives touts higher sequential-read and -write speeds than its predecessor.

products, such as the X25-M series, also employed SATAsystem-interface IP (intellectual property) from Marvell. Intel's expertise came into play at the other end of the SATA-logic block, extending to the embedded flash-memory array.

A notable downside of Intel's earlier-generation, 3-Gbps SATA-based solid-state drives was their comparatively slow sequential-write performance versus competitors' products. Judging from the 500-Mbyte/ sec sequential-read and 315-Mbyte/sec sequential-write speed claims for the highercapacity, 250-Gbyte 510 series variant, the company has heard and responded to the grumbling. Sequential-read and -write specifications for the 120-Gbyte product are 400 and 210 Mbvtes/sec. respectively, presumably due to the fact that the controller can simultaneously access fewer storage-array components and the blocks within those components. And the transition from 3- to 6-Gbps SATA also has a notable effect on sequential-access performance: When the 250-Gbyte solid-state drive connects to a 3-Gbps SATA bus, the drive specifies sequential-read and -write speeds of 265 and 240 Mbytes/sec, respectively, whereas its 120-Gbyte sibling clocks in at 265 and 200 Mbytes/sec, respectively. Now in production, the 250- and 120-Gbyte versions of the 510 series sell for \$584 and \$284 (1000), respectively.

-by Brian Dipert **⊳Intel Corp**, www.intel.com.

# LED ARRAY ENABLES SMALL-FORM-FACTOR MR-16 REPLACEMENTS

In the United States, it's easy to see the world of LED lighting through Edison-bulb-illuminated glasses, but these bulbs are not the dominant global light sources. Europe, for example, has more than 1 billion 35 to 50W MR-16 halogen lights, about 2 inches long and selling for about \$12 each. With the replacement market for these LEDs in mind. Cree recently introduced the MT-G LED array. It combines the company's EasyWhite color-mixing technology, a thermal resistance of 1.5°C/W, and efficacy as high as 92 lm/W (560 lm at 6W) at 85°C (3000K) in a 9.1×9.1mm footprint.

These devices let you design an MR-16 light with one LED, packing the LED, a secondary optic, the power-management circuit, and a heat sink into the MR-16 form factor. Cree has published a reference design, including power-control circuits.

-by Margery Conner Cree, www.cree.com.

The MT-G LED array offers

# **DILBERT By Scott Adams**

# Researchers claim millimeter-scale computing system

esearchers from the University of Michigan have made notable progress toward mainstream millimeterscale computing. The researchers at February's ISSCC (International Solid-State Circuits Conference) discussed a prototype implantable eye-pressure monitor for glaucoma patients that contains a complete millimeter-scale computing system. The researchers also discussed a compact radio that needs no tuning to find the right frequency and that they say could be a key enabler to organizing millimeter-scale systems into wireless sensor networks.

The researchers believe that millimeter-scale systems could enable ubiquitous computing. They point to Bell's Law, which states that a new class of smaller, cheaper computers emerges approximately once per decade. With each new class, the volume shrinks by two orders of magnitude and the number of systems per person increases. Researchers note that the law has held from 1960s' mainframes through the 1980s' PCs, the 1990s' notebooks, and the new millennium's smartphones.

"When you get smaller-thanhandheld devices, you turn to these monitoring devices," says David Blaauw, a professor in the university's department of electrical engineering and computer science. "The next big challenge is to achieve millimeter-scale systems, which have a host of new applications for monitoring our bodies, our environment, and our buildings. Because they're so small, you could manufacture hundreds of thousands on one wafer. There could be tens to hundreds of them per person, and this per-

University of Michigan researchers developed a millimeter-scale computing system, which targets use in an implantable eye-pressure monitor (courtesy Cyouho Kim).

capita increase fuels the semiconductor industry's growth."

The pressure monitor comes in a slightly larger than 1-mm³ package and fits an ultra-low-power microprocessor, a pressure sensor, memory, a thin-film battery, a solar cell, and a wireless radio with an antenna. It should become commercially available within several years.

"This is the first true millimeter-scale complete computing system," says Professor Dennis Sylvester. "Our work is unique in the sense that we're thinking about complete systems in which all the components are low-power and fit on the chip. We can collect data, store it, and transmit it. The applications for systems of this size are endless."

The processor in the eyepressure monitor is the third generation of the researchers' Phoenix chip, which uses a power-gating architecture and an extreme-sleep mode to achieve ultra-low power consumption. The newest system wakes every 15 minutes to take measurements and consumes an average of 5.3 nW. Keeping the battery charged requires exposure to 10 hours of indoor

light per day or 1.5 hours of sunlight. It can store a week's worth of information.

The researchers note that the system's radio cannot converse with other similar devices, so they have developed a consolidated radio with an onchip antenna that needs no bulky external crystal, which two isolated devices currently use when they need to communicate. The crystal reference keeps time and selects a radio-frequency band. The process of integrating the antenna and eliminating this crystal significantly shrinks the radio system, the researchers say. They integrate the antenna through an advanced CMOS process, allowing the engineers to precisely control its shape and size and therefore how it oscillates in response to electrical signals.

"Antennas have a natural resonant frequency for electrical signals that is defined by their geometry, much like a pure audio tone on a tuning fork," says David Wentzloff, assistant professor. "By designing a circuit to monitor the signal on the antenna and measure how close it is to the antenna's natural resonance, we can lock the transmitted signal to the antenna's resonant frequency."

"This is the first integrated antenna that also serves as its own reference," Wentzloff adds. "The radio on our chip doesn't need external tuning. Once you deploy a network of these [antennas], they'll automatically align at the same frequency." The researchers are working to lower the radio's power consumption so that it is compatible with millimeter-scale batteries.

—by Suzanne Deffree **University of Michigan**, www.umich.edu.

# AVX offers Spice models for tantalum, niobium-oxide capacitors

AVX Corp has expanded the capabilities of its SpiTanIII software to enable designers to view all basic characteristics and parameters for tantalum and Oxicap (niobium-oxide) capacitors. The company has also introduced a new S-parameter library in Version 1.1, which includes s2p (two-port-data) files. AVX is offering models for Microsim and OrCAD PSpice as well as for OrCAD Capture schematic parts.

SpiTanIII Version 1.1 allows designers to choose a desired component by part number or by categories, including capacitance, rated voltage, case size, or series. The software displays all basic parameters for selected capacitors, such as the frequency characteristics of capacitance, ESR (equivalent series resistance), impedance, DF (dissipation factor), and ripple-current and ripple-voltage ratings. It also allows users to examine leakage-current DCL (dc-leakage)-versus-time progress and an equivalent circuit diagram and displays values of all elements. Users can export all graphs as either images or data for further evaluation.

SpiTanIII Version 1.1 includes part numbers of various SMD chip-capacitor series that debuted in 2010, and the software database features high-reliability and -performance wet tantalum-axial capacitors. You can download the software at www.avx.com/spiapps/spitan/SpiTanIII\_V1.1.exe. For more news from AVX, go to http://bit.lv/hDoRoE.

−by Paul Rako►AVX Corp, www.avx.com.

# Eight-channel analog multiplexer meets high-reliability military specs

ishay Intertechnology recently expanded its family of MIL-PRF (military-performancespecification)-38535-screened analog switches and multiplexers with the release of the high-reliability, eight-channel, single-ended DG408 analog multiplexer. The device features a 44V maximum supply rating, on-resistance of  $100\Omega$ , and charge injection of 20 pC. The DG408's Enable pin allows you to use multiple devices to increase the number of input signals in an application.

The DG408 joins the previously released DG409 as a product that meets this new certification. Targeting use in high-speed data acquisi-

The eight-channel, single-ended DG408 analog multiplexer features a 44V maximum supply rating, on-resistance of  $100\Omega$ , and charge injection of 20 pC.

tion, audio-signal routing, and battery-powered and remote instrumentation, the device connects one of eight inputs to a common output, which a 3-bit binary address determines. Vishay's additional high-reliability capabilities include Group A, Group B, Group C, and Group E testing. In addition, Vishay continues to offer source-controlled drawing capabilities to allow space- and avionic-level screening. Sourcecontrolled drawing capabilities allow space- and avionic-level screening.

The device comes in a choice of military-package options, including a 16-pin CerDIP, a 20-pin LCC, and a 16-pin flat-pack. Samples and production quantities of the DG408AK multiplexer in the 16-pin CerDIP are available now; sample and production quantities of the DG408AZ in the 20-pin LCC and the DG408AL in the 16-pin flatpack will be available this quarter. Prices start at \$168.

−by Paul RakoVishay Intertechnology,www.vishay.com.

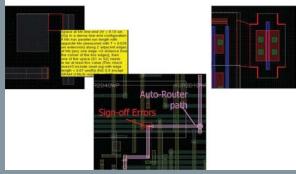

# Tool for custom-IC design allows verification in real time

Mentor Graphics' new Calibre RealTime platform allows designers to execute physical verification in real time during IC-layout creation. The first release provides instantaneous DRC (design-rule checking) in the SpringSoft (www.springsoft.com) Laker Version OA

You can use Calibre RealTime to detect and define sign-off DRC errors during manual layout editing, automatic routing, or generation of automated P cells.

(Open Access) 2010.8 custom-IC-design and -layout tools, using the same Calibre decks as for a batch sign-off flow. A version of Calibre RealTime for the Mentor IC Station Version 10 custom-design environment will become available in June.

Calibre RealTime executes direct calls to Calibre analysis engines running foundry-qualified rule decks. User-defined custom filters allow designers to limit which checks to run, depending on design requirements and organizational processes, without modifying the foundry-qualified rule deck. When you integrate Calibre RealTime into a custom-IC-design and -layout system, the tool's engines perform incremental checking near the shapes you are editing, providing immediate feedback on design-rule violations. By running with the same rule set that you use for design sign-off, Calibre RealTime complements many layout editors' built-in checkers.

A built-in error-review tool bar in the layout-design environment enhances ease of use. In-memory checking optimizes performance. By combining Calibre RealTime with batch Calibre and Calibre RVE (results-viewing environment), layout designers can minimize the need for full-chip verification runs, shortening the production schedule. Joseph Sawicki, vice president and general manager of the design-to-silicon division of Mentor Graphics, says that the OA runtime model will enable integration with most custom design environments, including Cadence Virtuoso.

-by Mike Demler

Mentor Graphics Corp, www.mentor.com.

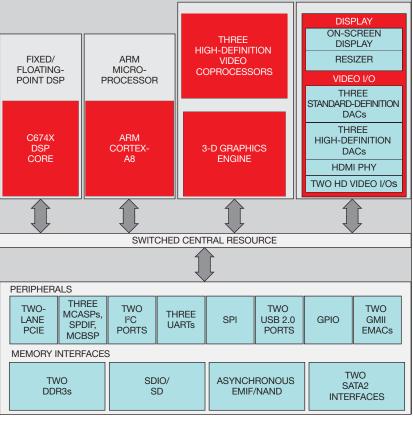

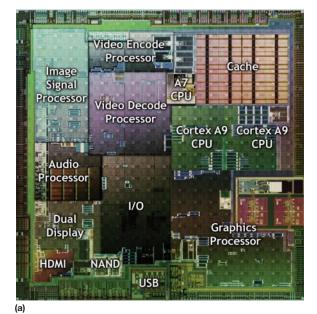

# Lithography reduction yields design simplicity

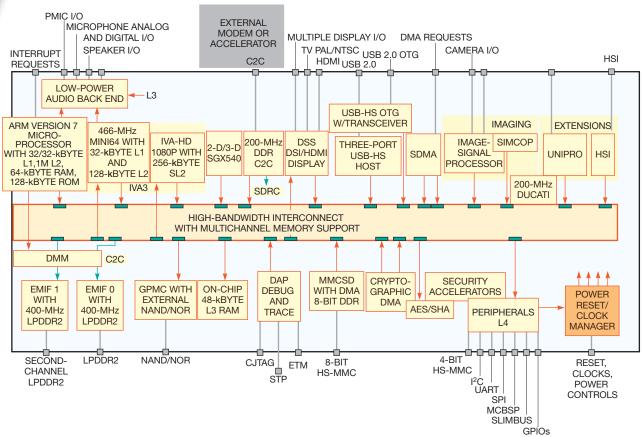

exas Instruments last month unveiled its ARM-based DaVinci-branded ICs. The video-focused TMS320DM816x is the first DaVinci-categorized product that TI built on a 40-nm lithography; its precursors use 65- and 90-nm processes. Like TI's Integra, they combine a Cortex-A8 CPU core and a C674x DSP core. The integrated peripheral mix is also similar to that of Integra, including PCIe (Peripheral Component Interconnect Express) Generation 2, SATA (serial-advanced-technology-attachment) 2.0, GbE (gigabit Ethernet), HDMI (highdefinition multimedia interface), CAN (controller-area-network) transceivers, and DDR2/DDR3-memory controllers. Targeting applications such as video-surveillance systems, TI embeds video-optimized circuitry for encoding, decoding, transcoding, digital-to-analog translation, and other imageprocessing tasks.

Integration yields 50% BOM-cost and one-fifth board-space reductions.

Differentiating the members of the TMS-320DM816x family is the presence or absence of the PowerVR SGX530 3-D graphics engine, the clock frequency—1 GHz for the entire device or 720 MHz for the CPU and 667 MHz for other areas of the chip—and whether they have two or three HD (high-definition) video decoders. Each IC processes as many as three simultaneous 1080p, 1920×1080-pixel-resolution, progressive-scan, 60-frame/sec H.264 video streams. TI does not specify the bit rate. They also process 12 simultaneous 720p, 30-frame/sec video streams or a combination of lower-resolution streams.

A lower-end version, the TMS320DM-8147, has no 3-D graphics core, whereas the TMS320DM8148 has a 3-D-augmented graphics core. They both run the ARM Cortex-A8 at 1 GHz, and the remainder of the chips operate at 750 MHz. Targeting 3W power consumption, the battery-powered devices can tackle a 1080p, 60-frame/sec video stream; three simultaneous 720p, 30-frame/sec video streams;

or multiple lower-resolution streams.

Tl anticipates future DaVinci family members that will be able to run the CPU and DSP at frequencies as high as 1.2 and 1 GHz, respectively. The company claims that the products' highly integrated nature reduces the system BOM (bill-of-materials) cost by 50% and decreases board space by one-fifth. Both products eliminate the need for previously required discrete components and halve the

aggregate circuitry's power consumption.

DM8168 processors are now available for sampling, and prices begin at \$75 (1000). The company expects the DM8148 family to become available for sampling in the third quarter, with prices starting at \$51 (1000). To is now shipping the \$1995 TMDXEVM8168 evaluation module; the free EZ SDK (software-development-kit) download currently supports Linux-based operating systems. To has scheduled Android support for the second quarter and Microsoft Windows Embedded Compact 7 support for the third quarter.—by Brian Dipert

▶**Texas Instruments**, www.ti.com.

DDR: DOUBLE DATA RATE DSP: DIGITAL-SIGNAL PROCESSOR EMAC: ETHERNET MEDIA-ACCESS CONTROLLER

EMIF: EXTERNAL-MEMORY INTERFACE GMII: GIGABIT MEDIA-INDEPENDENT INTERFACE

GPIO: GENERAL-PURPOSE INPUT/OUTPUT HD: HIGH DEFINITION HDMI: HIGH-DEFINITION MULTIMEDIA

INTERFACE

I/O: INPUT/OUTPUT I<sup>2</sup>C: INTER-INTEGRATED CIRCUIT MCASP: MULTICHANNEL AUDIO SERIAL PORT MCBSP: MULTICHANNEL BUFFERED SERIAL PORT PHY: PHYSICAL LAYER

SATA: SERIAL ADVANCED TECHNOLOGY

ATTACHMENT SD: SECURE DIGITAL SD: STANDARD DEFINITION

SDIO: SECURE DIGITAL INPUT/OUTPUT SPI: SERIAL-PERIPHERAL INTERFACE

3-D: THREE DIMENSIONAL

UART: UNIVERSAL ASYNCHRONOUS TRANSMITTER/RECEIVER USB: UNIVERSAL SERIAL BUS

The video-focused TMS320DM816x combines a Cortex-A8 CPU core and a C674x DSP core. Peripherals include PCIe Generation 2, SATA 2.0, GbE, HDMI, CAN transceivers, and DDR2/DDR3-memory controllers.

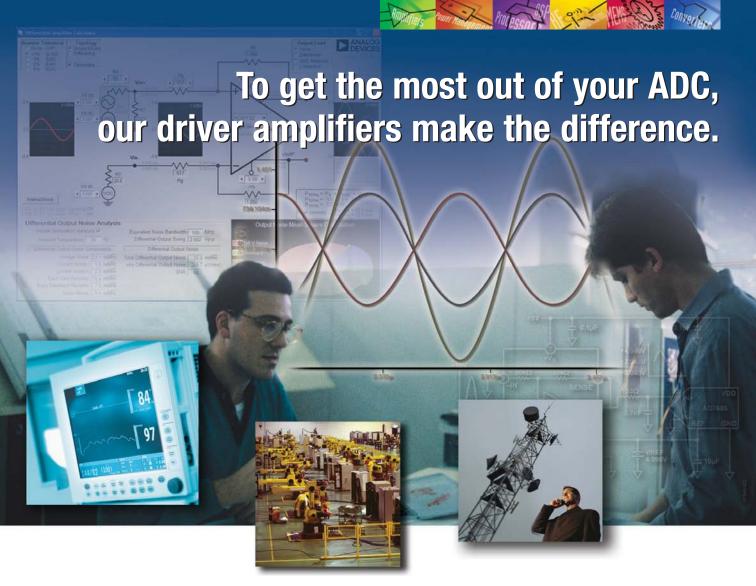

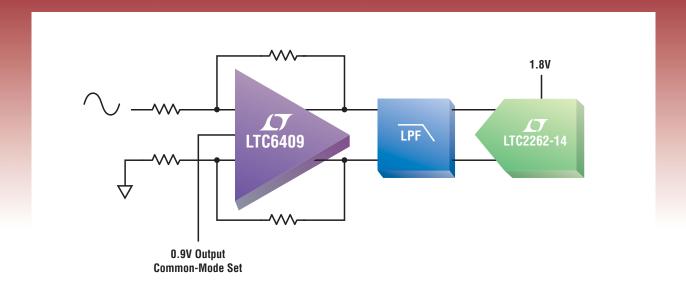

### A Driver for Every ADC

#### **Low Power Differential ADC Driver**

**ADA4932**—For true 14-bit applications to 20 MHz, or true 12-bit applications to 50 MHz. Supports single and differential inputs; only 9.6 mA quiescent current.

Ultralow Distortion, Current Feedback Differential ADC Driver ADA4927—For driving ADCs in high gain configurations up to  $20\times$ . Supports 14-bits of resolution from dc to 100 MHz.

### Level Translation, 16-Bit ADC Driver

**AD8275**—Integrated solution for driving precision, low voltage, single-ended, 16-bit ADCs up to 250 kSPS in  $\pm 10$  V applications. Attenuates and level shifts input signals. Eliminates multiple parts and simplifies implementation.

# **Differential RF/IF Amplifiers**

ADL5561/ADL5562—Highest linearity, lowest distortion amplifiers for driving 12-bit to 16-bit ADCs up to 500 MHz. Enable fully differential or single-ended-to-differential drive, with added flexibility of integrated on-chip user-selectable gain settings.

# Amplifiers that optimize your design

You've worked hard to get the right level of performance out of your ADC, now make sure your input driver does the same. ADI's differential amp drivers deliver clean, low distortion inputs to your converter so it can operate at peak performance. Who better to turn to for these devices than the leader in signal processing, Analog Devices? In fact, we created the category of ADC drivers and offer the most options—from online design tools that help with the selection, evaluation, and troubleshooting of your circuit to the industry's broadest selection of ADC driver components.

Make your ADC driving challenge easier at <a href="https://www.analog.com/ADCdriver">www.analog.com/ADCdriver</a>.

# SIGNAL INTEGRITY

# BY HOWARD JOHNSON, PhD

# Whang that ruler

lamp a wooden ruler to your desktop so that it overhangs the edge of the desk by about 8 inches. Now, flick the end of the ruler (Figure 1). It resonates, doesn't it? You can easily change the resonant frequency. Tape a few quarters to the end of the ruler and observe that the resonant frequency decreases. Shorten the length of overhang and hear it increase. If you push the resonant frequency high enough, it becomes difficult to stimulate the resonance with the soft end of your fingertip. Overcome that difficulty by depressing the end of the ruler with your finger in a way that lets the ruler slip off the hard edge of your fingernail.

At the risk of annoying your coworkers, whang the ruler over and over while you adjust the amount of overhang until you get a nice, musical resonance at about 100 Hz. Now, disconnect the clamp and hold the same length of ruler in your hand. Flick the end. Try to create the same resonant effect. I bet you can't do it.

When you clamp the ruler to the desktop, the clamp creates a low, mechanical impedance at one end of the ruler. The other end of the ruler remains free to move—the only limit being air resistance. Your stimulation creates a mechanical wave that bounces back and forth between these two endpoints, neither of which absorbs much of the mechanical energy. It therefore takes many back-and-forth cycles for the ruler to settle down. You have created a highly resonant system.

When you hold the ruler in your hand, the mechanical impedance of your hand lies close to the natural characteristic impedance of the ruler. Even if it is not a perfect match, your hand absorbs a significant portion of the energy in each cycle. The result is that the ruler cannot resonate.

The ruler supports transverse mechanical waves in just two directions: from one end of the ruler to the other

Figure 1 Whanging a clamp-attached ruler causes it to oscillate for many cycles before settling down.

and back again. Mechanical engineers call that phenomenon 1-D wave propagation. For any system like this one, an absorbing device at either end can totally damp the oscillations. Mechanical engineers use hydraulic shock absorbers, friction, air resistance, and rubber to absorb energy and create damping. Electrical circuits use resistive terminations.

A more complex system, such as a child's Indian drum, supports wave motion in two dimensions. Waves on the surface of the drumhead spread and reflect in many highly varied and complex patterns. An absorbing device

at just one location fails to damp the drumhead. To completely silence the drum, you must either apply absorbing material around a large fraction of the circumference or ask the child to please stop whanging. Good luck with that tactic.

PCB (printed-circuit-board) traces in a simple, linear topology behave as a 1-D-wave-propagation medium. If the trace is long enough and if it lacks any good energy-absorbing devices, it will resonate, distorting your signals.

When I say a trace has a simple, linear topology, I mean that it is a point-to-point connection or, at most, a linear-bus structure with multiple transceivers arrayed along a single trace. More complex structures, such as H distributions, star clusters, or random hairball nets, support multiple modes of oscillation and may, like a drumhead, require terminations in multiple locations.

When I say "long enough," I mean that the end-to-end trace delay is a significant fraction of the signal rise or fall time. A delay as long as one-sixth the rise or fall time is significant, especially if the trace has a particularly low-impedance driver or a large capacitive load. I simulate all such traces. Keep in mind that even short traces resonate; the resonant frequency is just so high that you may not observe its effect using logic with a particular rise and fall time. Applying logic with faster edges to the same trace might make it ring, just as flicking the ruler with your fingernail stimulates resonance at a small length.

Applying a capacitive load to a PCB trace has much the same effect as a load of quarters on the end of the ruler: It lowers the resonant frequency of the structure, making it more likely that you will notice its effects.**EDN**

Howard Johnson, PhD, of Signal Consulting, frequently conducts technical workshops for digital engineers at Oxford University and other sites worldwide. Visit his Web site at www.sigcon.com, or e-mail him at howie03@sigcon.com.

# Your Project Acceleration Resource for Electronics Manufacturing

# Electronics

# February 14-16, 2012

Anaheim Convention Center Anaheim, CA

ElectronicsWestShow.com

# Electronics

# May 2-3, 2012

Charlotte Convention Center Charlotte, NC

**Electronics-South.com**

# Electronics

# April 25-26, 2012

Boston Convention & Exhibition Center Boston. MA

Electronics-NE.com

Find the suppliers, tools, and services you need to make your product, process, and business more efficient, cost-effective, and profitable.

For information on attending or exhibiting, please call 310/445-4200 or visit CanonTradeShows.com

WHETHER YOU ARE DESIGN-ING OR BUYING A DIGITIZ-ING SYSTEM, YOU NEED SOME MEANS OF DETERMINING REAL-LIFE PERFORM-ANCE. HOW CLOSELY DOES THE OUTPUT OF ANY ADC, WAVEFORM DIGITIZER, OR DSO FOLLOW AN ANALOG INPUT SIGNAL? ENOB TESTING PROVIDES A MEANS OF ESTABLISHING A FIGURE OF MERIT FOR DYNAMIC DIGITIZING PERFORMANCE.

ne of the most common sources of errors in measurements is the presence of vertical noise, which can decrease the accuracy of signal measurement and lead to such problems as inaccurate measurements as frequencies change. You can use ENOB (effective-number-of-bits) testing to more accurately evaluate the performance of digitizing systems, including oscilloscopes. The ENOB figure summarizes the noise and frequency response of a system. Resolution typically degrades significantly as frequency increases, so ENOB versus frequency is a useful specification. Unfortunately, when an ENOB specification is provided, it is often at just one or two points rather than across all frequencies.

In test and measurement, noise can make it difficult to make measurements on a signal in the millivolt range, such as in a radar transmission or a heart-rate monitor. Noise can make it challenging to find the true voltage of a signal, and it can increase jitter, making timing measurements less accurate. It also can cause waveforms to appear "fat" in contrast to analog oscilloscopes.

#### THE ENOB CONCEPT

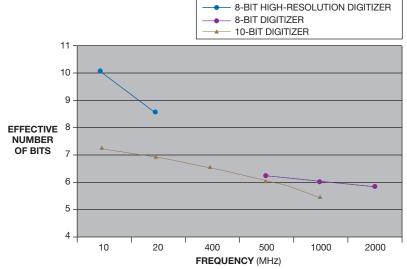

Digitizing performance is linked to resolution, but simply selecting a digitizer with the required number of bits, or quantizing level, at the desired amplitude resolution can be misleading because dynamic digitizing performance, depending on the technology, can decrease markedly as signal speeds increase. An 8-bit digitizer can decrease to 6, 4, or even fewer effective bits of performance well before reaching its specified bandwidth.

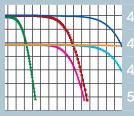

When designing or selecting an ADC, a digitizing instrument, or a test system, it is important to understand the various factors affecting digitizing performance and to have some means of evaluating overall performance. ENOB testing provides a means of establishing a figure of merit for dynamic digitizing performance. You can use it as an evaluation tool at various design stages and as a way to provide an overall system-performance specification. Because manufacturers don't always specify ENOB for individual instruments or system components, you may need to do an ENOB evaluation for comparison. Essentially, ENOB is a means of specifying the ability of a digitizing device or instrument to represent signals of various frequencies (Figure 1).

The **figure** illustrates that effective digitizing accuracy falls off as the frequency of the digitized signal increases. In this case, an 8-bit digitizer provides 8 effective bits of accuracy only at dc and low frequencies. As the signal you are digitizing increases in frequency or speed, performance drops to lower and lower values of effective bits.

This decline in digitizer performance manifests itself as an increasing level of noise on the digitized signal. Noise in this case refers to any random or pseudorandom error between the input signal and the digitized output. You can express this noise on a digitized signal in terms

#### AT A GLANCE

- ENOB (effective number of bits) is a general figure of merit for signal integrity in scopes and represents the cumulative errors across a frequency range.

- In general, the ENOB figure decreases as frequency increases.

- You should carefully evaluate ENOB performance, especially for applications involving high bit rates and fast edges.

of SNR (signal-to-noise ratio): SNR= rms<sub>SIGNAL</sub>/rms<sub>ERROR</sub>, where rms<sub>SIGNAL</sub> is the root-mean-square value of the digitized signal and rms<sub>ERROR</sub> is the root-mean-square value of the noise er-

ror. The following equation yields the relationship to effective bits:  $EB=\log_2(SNR)-1/2\log_2(1.5)-\log_2(A/FS)$ , where EB represents the effective bits, A is the peak-to-peak input amplitude of the digitized signal, and FS is the peak-to-peak full-scale range of the digitizer's input. Other commonly used equations include  $EB=N-\log 2(rms_{ERROR})/1DEAL\_QUANTIZATION\_ERROR)$ , where N is the nominal, or static, resolution of the digitizer, and,  $EB=-\log_2(rms_{ERROR})/12/FS$ .

These **equations** employ a noise, or error, level that the digitizing process generates. In the second **equation** above for EB, the ideal quantization error term is the rms error in the ideal, N-bit digitizing of the input signal. The IEEE Standard for Digitizing

Figure 1 When comparing digitizer performance, it is important to test the full frequency range.

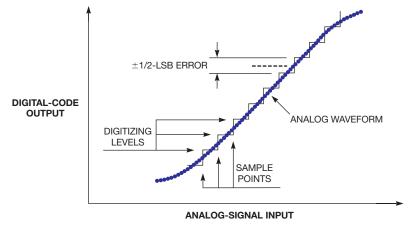

Figure 2 Quantizing errors are inherent parts of digitization.

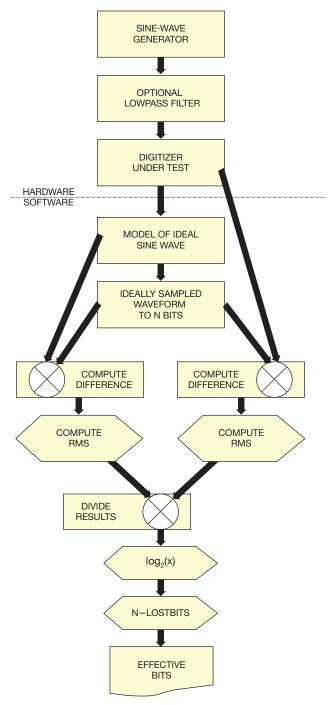

Figure 3 Measuring the ENOB figure involves applying a known, high-quality signal to the digitizer and then analyzing the digitized waveform.

Waveform Recorders (IEEE Standard 1057) defines the first two **equations** (Reference 1). An alternative for the third **equation** assumes that the ideal quantization error is uniformly distributed over one LSB (least-significant bit) peak to peak. This assumption allows you to replace the ideal quantization error term with  $FS/(2^N\sqrt{12})$ ,

where FS is the digitizer's full-scale input range.

These equations employ full-scale signals. Actual testing may use test signals at less than full-scale—50 or 90% of full-scale, for example. Improved ENOB results can improve this result, so comparisons of ENOB specifications or testing must account for both

test-signal amplitude and frequency.

Noise or error relating to digitizing can come from a number of sources. Even in an ideal digitizer, quantizing causes a minimum noise or error level amounting to  $\pm \frac{1}{2}$  LSB. This error is an inherent part of digitizing (Figure 2). It is the resolution limit, or uncertainty, associated with ideal digitizing. A reallife digitizer adds further errors to this basic ideal error floor. These additional real-life errors can include dc offset; ac offset, or "pattern" errors, sometimes called fixed pattern distortion, associated with interleaved sampling methods; dc and ac gain error; analog nonlinearity; and digital nonmonotonicity. You must also consider phase errors; random noise; frequency-timebase inaccuracy; aperture uncertainty, or sample-time jitter; digital errors, such as data loss due to metastability, missing codes, and the like; and other error sources, such as trigger jitter.

### **ENOB MEASUREMENT**

Beyond these error sources, still other possible sources of digitizing error exist. For example, in high-speed real-time digitizing without sample-and-hold or track-and-hold tracking, the LSBs must change at high rates to follow a quickly changing signal. This requirement increases bandwidth requirements for data lines and buffer inputs for these lesser bits. If you do not meet bandwidth requirements, quickly changing lesser bits can be dropped, lowering the ENOB.

It is often easier to measure overall performance instead of trying to distinguish and measure each error source in a digitizing system. A good place to start is by determining the digitizing system's SNR and the resulting effective bits according to the preceding equations. This approach provides an easily understood and universal figure of merit for comparisons.

The basic test process involves applying a known, high-quality signal to the digitizer and then analyzing the digitized waveform (Figure 3). The test uses a sine wave as the test signal because high-quality sine waves are relatively easy to generate and characterize. The general test requirements are that the sine wave generator's performance must significantly exceed that of the digitizer under test. Otherwise, the test will be unable to distinguish digitizing

Figure 4 The oscilloscope does not display the extreme ranges of noise because they occur quickly and infrequently, and the resulting trace is thin.

errors from signal-source errors. It may be necessary to add filters to the source to reduce source harmonics to levels significantly below what you might expect from the digitizer under test.

To obtain an ENOB, you must compute a perfect, or idealized, sine wave and apply it to your oscilloscope, fitting it to the digitized sine wave. This approach simulates what the N-bit digitizer under test would produce if it were an ideal N-bit digitizer. You then compute the difference between the com-

# IT IS OFTEN EASIER TO MEASURE OVER-ALL PERFORMANCE INSTEAD OF TRYING TO MEASURE EACH ERROR SOURCE IN A DIGITIZING SYSTEM.

puted ideal sine wave and the perfectly sampled and digitized version. The rms value of this difference provides the ideal quantization error. You obtain the rms-error value in the ENOB equations by subtracting the ideal sine wave from the actual digitized sine wave and finding the rms value of the result. Alternatively, you can find the rms value of the signal and the rms error and use them to compute SNR. The final computation results in an ENOB for the digitizer. By keeping the input signal's amplitude constant for various frequencies, you can further compute ENOBs for the subject digitizer or digitizing system. You can plot these numbers against frequency to obtain a digitizer performance curve.

ENOB measurement combines the key digitizer system errors into a figure of merit that is easy to understand

Figure 5 A DSO trace appears thicker than the analog scope's trace because every hit has the same intensity.

and use in comparisons. ENOB depends on the input signal's percentage of full-scale digitizer amplitude. Testing a digitizer at less than full-scale amplitude generally yields a somewhat better ENOB figure than does testing it at full-scale. Whatever test approach you use—full-scale or partial scale—the input test signal's amplitude specification should accompany the results.

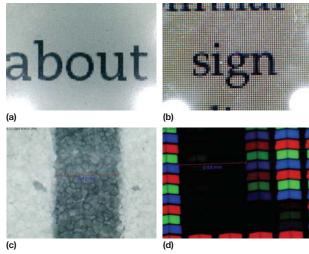

### **SCOPE NOISE**

When comparing digital oscilloscopes with analog oscilloscopes, a common misperception is that digital oscilloscopes have a higher level of vertical noise. With digital oscilloscopes, the trace may appear fatter than that

Figure 6 A DPO trace displays the signal based on the frequency of the hits.

of its analog-oscilloscope equivalent. A digital oscilloscope does not have higher noise levels than the equivalent analog oscilloscope, however; it just appears that way.

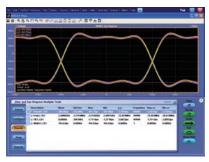

Analog oscilloscopes with CRT displays do not display the extreme ranges of noise because they occur quickly and infrequently (Figure 4), meaning that the phosphor lights quickly and infrequently, and those extremes are dim or not on the screen at all. Analog instruments do not just display voltage versus time but have a third dimension: intensity. Intensity relates to the frequency of occurrence of the signal. A DSO (digital-signal oscilloscope) shows every hit with the same intensity, no matter the frequency of pixel hits (Figure 5). DPOs (digital-phosphor oscilloscopes)

Figure 7 A test applies a 6.5-GHz sine wave to a DPO with 13-GHz bandwidth and 400-mV full-scale amplitude. The DPO also has infinite display persistence to show variations across all acquisitions.

offer a way to restore that third dimension by grading the signal employing the frequency of the hits (Figure 6).

### **REAL-WORLD SIGNAL NOISE**

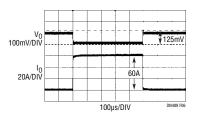

ENOB performance indicates noise that has an effect on both amplitude and timing measurements. To illustrate the effects of noise on amplitude, a test applied a 6.5-GHz sine wave to a Tektronix (www.tektronix.

Figure 8 This result from Figure 7's test corresponds to approximately 5.9 ENOBs at 6.5 GHz.

com) DPO/DSA70000B oscilloscope with a 13-GHz bandwidth and a 400-mV full-scale voltage. It also has infinite display persistence so that you can see variations across all acquisitions. With no averaging, the test run included approximately 10,000 acquisitions. The result is approximately 15.9 mV of trace thickness at the peak, representing 3% of full-scale on this oscilloscope

(Figure 7). This result corresponds to approximately 5.9 ENOBs at 6.5 GHz (Figure 8). Comparative testing shows other oscilloscopes with more than 35-mV trace thickness at the peak and approximately 4.5 ENOBs using identical test setups.

# **ENOB EFFECTS**

ENOB effects can also be seen on

# See Aeroflex performance in action.

See how we did it - download our speed vs phase noise technical note and view our video at www.aeroflex.com/edn0411 or call 1-800-836-2352.

# The S-Series

Aeroflex introduces the signal generator of the future, and makes compromise a thing of the past.

With a legacy of innovation that includes pioneering the use of Fractional-N synthesizers originally developed by Marconi Instruments, Aeroflex sets a new standard for performance, versatility, and ease of use with the SGA analog RF signal generator.

Compact and lightweight with an intuitive touchscreen interface, the SGA offers best-in-class precision, productivity, and reliability — all at a surprising mid-range price.

- Test both high quality receivers and devices faster. Typical phase noise is -135 dBc/Hz at 20 kHz offset from a 1 GHz carrier. You can easily measure receiver selectivity beyond 80 dB.

- Accelerate production throughput.

Frequency settling times range from 1 ms to 100 µs up to 5X faster than comparable signal generators.

- Have answers at your fingertips, not buried in menus.

The elegant touchscreen interface requires fewer commands, saves time, and prevents errors.

Figure 9 ENOB performance affects both amplitude and jitter on the eye diagram.

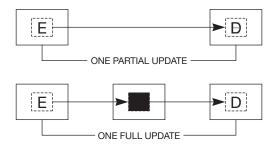

eye diagrams. ENOB performance affects both amplitude and jitter on the eye. A 5-Gbps eye diagram represents a signal bit rate that is associated with PCIe (Peripheral Component Interconnect Express) Generation 2 or USB (Universal Serial Bus) 3.0 (Figure 9).

The test applies this signal to the Tektronix DPO70000B oscilloscope, with the instrument set up to measure TIE (time-interval-error) jitter, affecting both jitter and amplitude noise. The measured jitter for this test was 3.08 psec p-p. In comparison testing, some oscilloscopes show more than 11 psec p-p on the same signal.

Similarly, noise also affects the eye's amplitude. In this case, a measurement of the eye height at the 50% point of the eye shows approximately 582-mV amplitude. This result compares with less than 525 mV measured on other instruments.

All digitizing systems have noise that only gets worse as speeds increase. Therefore, it is useful to have a way to evaluate the real-life noise performance of digitizing systems, including test instrumentation. ENOB is a general figure of merit for signal integrity in any analog or digital system, representing the cumulative errors across a frequency range. Generally, the ENOB figure decreases as frequency increases.

You can easily see errors relating to lower ENOB performance in real-world signals as increased noise when performing amplitude measurements and increased jitter when making jitter measurements. As the ENOB figure decreases, the measurement precision of the instrument decreases, directly equating to the margin available for the tests you are performing on the instrument. With these factors in mind,

you should carefully evaluate ENOB performance, especially for applications involving high bit rates and fast edges. EDN

#### REFERENCE

"1057-1994, IEEE Standard for Digitizing Waveform Recorders," IEEE, 1994, http://bit.ly/eYo1NP.

#### **AUTHOR'S BIOGRAPHY**

Jit Lim is the senior technologist for high-speed signal analysis at Tektronix, where he has worked for 23 years. He has published numerous tech-

nical papers and holds a bachelor's degree in electrical engineering from the Massachusetts Institute of Technology (Cambridge, MA).

ARM AND ITS LICENSEES ARE STRIVING TO EXPAND THEIR OVERALL MARKET PRESENCE BY TACKLING INTEL'S x86 IN SERVERS AND CLIENT DESKTOP AND LAPTOP COMPUTERS. INTEL HAS RESPONDED BY ATTACKING ARM ON ITS OWN TURF: HANDSETS, TABLETS, AND THE LIKE.

BY BRIAN DIPERT . SENIOR TECHNICAL EDITOR

RM, along with its core licensees, and Intel, along with its x86 CPU competitors, have recently taken action to put to rest any remaining doubt that both camps were on a collision course—ARM touting its RISC (reduced-instruction-set-computer)-based technology and Intel backing the CISC (complex-instructionset-computer) approach. When Intel three years ago formally introduced the first-generation Atom processor family, the company made it clear that it was aiming not just at low-end desktop and notebook PCs but also at the handheld systems in which ARM had historically dominated. In response, ARM more recently unveiled the Cortex-A15 core, whose application targets extend up to the server segment in which Intel and AMD (Advanced Micro Devices) have long reigned supreme. And at the January 2011 CES (Consumer Electronics Show), Microsoft revealed its willingness to put a nail in the coffin of the Wintel alliance by broadening upcoming Windows 8's instruction-set compatibility to encompass both ARM and x86.

Since ARM unveiled the Version 7 instruction set, the company has subdivided its product line into three segments: the highly integrated Cortex-A application processors for mobile devices, cost-sensitive Cortex-M processors for traditional microcontroller applications, and high-performance Cortex-R processors for deeply embedded realtime applications. Cellular handsets, multimedia record-and-playback devices, and other portable electronics systems incur substantial product volume shipments. That fact, along with their direct competition with Intel-architecture processors, explains why this article focuses on ARM Cortex-A CPUs (see sidebar "Intel's potential multiphase response"). For more, see EDN's coverage of Cortex-M, Cortex-R, and alternative-market Cortex-A products, such as Ambarella's iOne (Reference 1).

# **ARMING FOR BATTLE**

Any discussion of ARM's potential success in currently x86-dominated ecosystems must begin with an understanding of ARM's business model and current product offerings. From a fiscal viewpoint, as an IP (intellectual-property) developer, ARM depends largely on the market success of its licensees, which fall into conventional- and architecture-license camps. Conventional licensees implement predesigned cores in their SOC (system-on-chip) designs, a more straightforward path to bringing products to market, which conversely limits each licensee's ability to differentiate its products from those of competitors. Architecture, or instruction-set, licensees, on the other hand, have more design flexibility but also incur incremental corresponding design challenges. Although they must, as their name implies, retain full ARM instruction-set backward compatibility, they can also build on that suite with proprietary instructions, as well as make other more fundamental circuit alterations and enhancements. ARM currently has few architecture licensees, including Intel, Marvell, Microsoft, Nvidia, and Qualcomm, for example.

As for the Cortex-A proliferations currently available to conventional licensees, the Cortex-A8 builds on the Cortex-A5 foundation, which many licensees bypassed in the transition from the ARM11. Cortex-A8 offers dual-issue superscalar support and deepens the per-core pipeline from eight to 13 stages as a means of boosting clock rates at the potential expense of IPC (instructionper-clock) efficiency. Cortex-A8 requires an upgraded FPU (floating-point unit), which was optional on ARM11. Cortex-A8 also requires the 64-bit, SIMD (single-instruction/multiple-data) Neon computing engine. Moving from that point to the ascendant Cortex-A9 involved several enhancement steps. Implementing Neon, an FPU, or both became a design-trade-off decision versus an implementation requirement. ARM shrunk the per-core pipeline to nine stages but retained morethan-1-GHz performance, thanks to lithography reductions, and out-of-order support further improved the average delivered IPC.

Conventional licensees' core-implementation constraints don't rule out

## AT A GLANCE

- ☑ ARM's conventional and architecture licensees have varying means of developing products employing the company's diverse instruction sets and cores.

- Nvidia has clearly broadened its corporate focus beyond or, depending on your perspective, away from PC graphics and toward the burgeoning ARM-SOC (system-onchip) market.

- Texas Instruments, late to the Cortex-A9 era, is determined to quickly and solidly regain its long-standing ARM momentum.

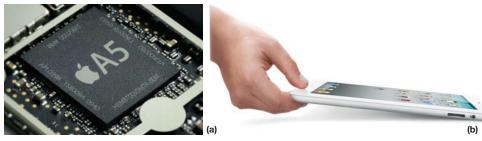

- Apple and Samsung direct their semiconductor groups' SOC outputs at their system divisions. Samsung does so with an inconsistent sourcing strategy, however.

- Qualcomm and Marvell are leveraging their architecture licenses to create differentiated ARMbased products.

notable innovations. Take, for example, the Fast14 dynamic-logic and signalencoding techniques that Samsung licensed from Intrinsity for use in Samsung's Cortex-A8-based Hummingbird SOC. After acquiring Intrinsity a year ago, Apple subsequently implemented those techniques in its Cortex-A8based A4 CPU. Fast14 enabled both Apple and Samsung, which also acted as the A4 SOC's foundry source, to obtain notably higher clock speeds at a given process node than other Cortex-A8 licensees could accomplish. Conversely, architectural licensee Qualcomm developed the ARM Version 7-compliant Scorpion architecture, which, initially on 65-nm lithography, is currently in 45 nm.

Scorpion achieved dual-core status in mid-2010 with the 1.2-GHz MSM8260 and MSM8660. Functionally, it is an intermediary step between Cortex-A8 and Cortex-A9, supporting some but not all of Cortex-A9's out-of-order instruction-execution capabilities. Scorpion-based Snapdragon SOCs also implement Cortex-A8- and A9-compliant floating-point and Neon SIMD engines. Scorpion implements the floating-point engine in a pipelined fashion, and the SIMD engine, at 128 bits, is

twice as wide as the one in Cortex-A9.

Two generic terms, "application processor" and "baseband processor," bear mentioning, although in practice they are becoming increasingly irrelevant, thanks to single-die integration trends. An application processor, as a seminal 2004 presentation from BDTI (Berkeley Design Technology Inc) describes, runs user applications, supports complex operating systems, emphasizes multimedia processing, supports Java and other virtual machines, and implements security features (Reference 2). The companion baseband processor, on the other hand, tackles wireless communications, including various cellular voice and data protocols.

Various ARM licensees have divergent perspectives on baseband- versus application-processor segmentation. Texas Instruments, for example, announced in October 2008 that it would phase out its participation in the baseband business, which it viewed as highly commoditized and therefore insufficiently profitable. Qualcomm, on the other hand, has embedded baseband capabilities within most of its Snapdragon CPUs, befitting the company's MSM (Mobile Station Modem, formerly OSD for Qualcomm Semiconductor) product-name prefix, although some basebandless APQ (Application Processor Qualcomm) devices also exist. Nvidia, conversely, has been adamant that it makes no sense to burden the silicon area or constrain the technology development of an application processor with baseband capabilities. It may also make little sense to put a cellular-cognizant application processor into, for example, an optionally or by-default Wi-Fi-only tablet-computer design, therefore explaining, for example, the dual-core 1.2-GHz Qualcomm APQ8060 in Hewlett-Packard's firstgeneration TouchPad tablet.

# A FOCUS ON MULTIMEDIA

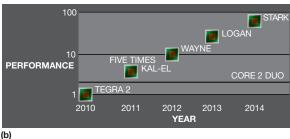

Nvidia obtained notable aspects of its ARM-SOC program through the acquisitions of MediaQ, which it announced in August 2003, and of PortalPlayer, which it announced in November 2006. The company's initial ARM11-based Tegra SOCs achieved limited market success, aside from being the processing nexus of Microsoft's Zune HD portable multimedia player

Figure 1 Nvidia's Tegra 2 SOC is seemingly the reference CPU for Google's Android 3.0 Honeycomb operating system in Motorola's Xoom tablet (a), but the integrated processor also finds use in modern high-end smartphones, such as Motorola's Atrix 4G (b), whose mating dock, display, and keyboard enable it to approximate a full PC experience (c). LG's Optimus 2X might use Tegra 2, but the newer Optimus 3D went with TI's OMAP 4 instead, due to its higher-resolution video-encoding support (d). RIM's BlackBerry PlayBook tablet is another OMAP 4 design win (e), whereas Samsung's

10.1-in. Galaxy Tab gave Tegra 2 the nod. The company's Galaxy S II smartphone bafflingly splits processor loyalties between Nvidia and Samsung's own semiconductor group (f). HP's TouchPad is a Qualcomm dual-core Snapdragon advocate (g).

and short-lived Kin cellular handset. The company bypassed both the Cortex-A5 and the Cortex-A8 generations to come up with its next-generation Tegra 2 products, which it formally unveiled at the January 2010 CES. A year ago, Nvidia had a somewhat-tarnished industry reputation because the raft of Tegra 2-based tablet computers and other devices that company Chief Executive Officer Jen-Hsun Huang claimed at CES would shortly materialize hadn't done so.

What a difference a year makes. Nvidia had achieved first-to-market status in the dual-core Cortex-A9 generation by several quarters versus competitors such as Texas Instruments. In doing so, it gained Google's nod in the reference design for tablet-targeted Android Version 3 Honeycomb (Figure 1). Several high-end smartphones that debuted at the 2011 iterations of CES and MWC (Mobile World Congress) in mid-Feb-

ruary also harness its capabilities, although its reported inability to decode high-profile 1080p H.264-encoded video led to its 11th-hour replacement in the Boxee set-top-box design by Intel's Atom-based CE4100 CPU. Similarly, LG chose a Texas Instruments OMAP (Open Multimedia Applications Platform) 4-based CPU for its Optimus 3-D handset, although Tegra 2 had received the nod in the Optimus 2X phone LG had introduced less than two months earlier. LG chose the OMAP 4 because TI's SOC could encode 3-D content in real time in 1080p resolution, whereas Nvidia's CPU had only 720p capabilities (references 3 and 4).

Tegra 2 comes in T20 and AP20 variants, encompassing the Tegra 230 and Tegra 250, respectively. Both CPUs run at 1 GHz, but the GPU (graphics-processing unit) in T20 uses a 333-MHz clock and DDR2 system memory, befitting the larger screens and batteries in

pickering

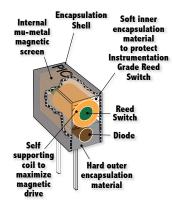

# Pickering Reed Relays

# Need Instrumentation Grade Reed Relays? Look No Further

Pickering Electronics is a Manufacturer of high quality Reed Relays for:

- Instrumentation

- Automatic Test Equipment (ATE)

- · High voltage switching

- Low thermal EMF

- · Direct drive from CMOS

- RF switching and other specialist applications.

# Only Pickering has SoftCenter™ Technology

Pickering Reed Relays are encapsulated using a soft inner material to protect the reed switch capsule. The very hard compounds used by most other manufacturers can cause stresses that can potentially damage the reed switch and degrade contact resistance stability and life expectation. Go to www.pickeringrelay.com to find out more....

pickeringrelay.com

tablets. Its handset-focused AP20 peer, in contrast, operates the GPU at 300 MHz and interfaces to the more-power-stingy LP (low-power) DDR2 SDRAM. Strictly speaking, it's a triple-ARM configuration because it also contains an ARM7 core for overall SOC management. You can suspend both Cortex-A9 cores, albeit not individually, when, for example, only the audio, imaging, graphics, and other dedicated processing resources are in use (Figure 2).

Nvidia leaked documentation in late January suggesting that it planned to announce AP25 and T25, or Tegra 2 3-D, during the first quarter of this year. Both variants upped the ARM core clock speed to 1.2 GHz, with GPU

speeds up to 400 MHz. It's now unclear, however, whether they'll ever see the light of day because the quad-core follow-on AP30 and T30 SOCs, or Tegra 3, code-named Kal-El, have also appeared, courtesy of an aggressive development cycle. Nvidia obtained first Kal-El samples from its foundry partner just 12 days before MWC, during which it was showing robust graphics and video demos running at 2560×1600-pixel resolutions, twice the per-frame pixel count of conventional 1080p video.

The target per-core Cortex-A9 clock speed for Kal-El is 1.5 GHz. Unlike Tegra 2, Kal-El embeds a Neon SIMD vector FPU for each CPU core. Like Tegra 2, however, Kal-El continues to rely on a unified 1-Mbyte pool of L2 cache memory, which twice as many CPU cores as before share, as well as a 32-bit system-memory interface. The Nvidia-designed GPU is not only faster in Kal-El than in Tegra 2 but also ups the core count from eight to 12. Both Tegra 2 and Kal-El employ a 40-nm manufacturing process, thereby explaining the die-size boost from 49 mm<sup>2</sup> on Tegra 2 to roughly 80 mm<sup>2</sup> on Kal-El. Nvidia's marketers believe that Kal-El will deliver roughly five times the aggregate speed of Tegra 2—twice the CPU performance and three times the graphics performance—and consume no more—and, in some cases, notably less—power on a workload-

# **INTEL'S POTENTIAL MULTIPHASE RESPONSE**

You might think, faced with ARM's formidable development road map and equally formidable laundry list of licensees, coupled with the loss of the x86 instruction-set lock in upcoming Windows 8, that Intel would be reeling and ready to retreat in its legacy stronghold computing markets. First, though, recall that the company has formidable semiconductor-manufacturing resources that it can apply to problems such as these, in the form of new process lithographies, which the foundries that most ARM licensees use find challenging to pace, and in the form of a multifab network. Last September, company officials explicitly stated their plans for a future move of Atom-based SOCs (systems on chips) down to at least the 15-nm process node, if not further.

Intel originally manufactured Atom on a 45-nm lithography in CPU form; the companion chip set used a 90-nm process. It has now progressed down to the 32-nm process level

in the form of the highly integrated Medfield chip set for handsets and Oak Trail chip set for tablets. Oak Trail offers full PCI (Peripheral Component Interconnect)-bus support for Windows 7 cognizance (Reference A). Intel's partnership with Nokia appears to be on the ropes due to Nokia's recent embrace of the Windows Phone 7 operating system to the exclusion of both legacy Symbian and Intel-codeveloped-and, presumably, x86-favoring-MeeGo. Nevertheless, Intel executives remain confident that **Medfield-based handsets** will enter production this year. Numerous system manufacturers are demonstrating Oak Trail-based tablets running both Microsoft-developed and alternative operating systems.

Instruction-set compatibility is seemingly decreasing in importance over time with consumers, due to the consolidating number of file formats that require support, the increasing number of OS-agnostic applications that compre-

hend those formats, and the growing trend of storing both applications and their data in the "cloud" rather than on client systems. However, instruction-set compatibility—specifically for x86—remains critically important for software developers, who prefer to reuse known functional code snippets and associated development tools whenever possible.